# **Signetics**

# 74LS568A, 569A 3-State Bidirectional Counters

'568A BCD Decade Up/Down Synchronous Counter (3-State) '569A 4-Bit Binary Up/Down Synchronous Counter (3-State) Product Specification

#### **Logic Products**

#### **FEATURES**

- Speed improved over LS568/ LS569

- Synchronous counting and loading

- UP/DOWN counting

- BCD decade counter

'5684

- Modulo 16 binary counter

'569A

- Two Count Enable inputs for n-bit cascading

- Positive edge-triggered clock

- Asynchronous Master Reset

- 3-State Counter outputs

- Gated Carry output

#### DESCRIPTION

The '568A and '569A are synchronous presettable UP/DOWN counters featuring an internal carry look-ahead for applications in high speed counting designs.

Synchronous operation is provided by having all flip-flops clocked simultaneously so that the outputs change coin-

| ТҮРЕ     | TYPICAL f <sub>Max</sub> | TYPICAL SUPPLY CURRENT (TOTAL) |

|----------|--------------------------|--------------------------------|

| 74LS568A | 35MHz                    | 28mA                           |

| 74LS569A | 35MHz                    | 28mA                           |

#### ORDERING CODE

| PACKAGES    | COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V ±5%; T <sub>A</sub> = 0°C to +70°C |

|-------------|-----------------------------------------------------------------------------|

| Plastic DIP | N74LS568AN, N74LS569AN                                                      |

#### NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS                            | DESCRIPTION | 74LS   |

|---------------------------------|-------------|--------|

| All                             | Inputs      | 1LSul  |

| Q <sub>0</sub> - Q <sub>3</sub> | Outputs     | 30LSul |

| TC, GC                          | Outputs     | 10LSul |

#### NOTE:

A 74LS unit load (LSul) is 20 µA IIH and -0.4mA IIL.

cident with each other when so instructed by the Count-Enable inputs and internal gating. This mode of operation eliminates the output spikes which are nor-

mally associated with asynchronous (ripple clock) counters. A buffered Clock input triggers the flip-flops on the LOW-to-HIGH transition of the Clock.

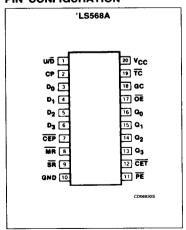

#### PIN CONFIGURATION

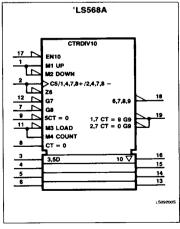

### LOGIC SYMBOL

### LOGIC SYMBOL (IEEE/IEC)

December 4, 1985

5-577

853-0491 81500

# 74LS568A, 569A

#### PIN CONFIGURATION

The counter is fully programmable; that is, the

outputs may be preset to either level. Preset-

ting is synchronous with the Clock, and takes

place regardless of the levels of the Count

Enable inputs. A LOW level on the Parallel

Enable (PE) input disables the counter and

causes the data at the Dn inputs to be loaded

into the counter on the next LOW-to-HIGH

transition of the Clock. The Synchronous

Reset (SR), when LOW one set-up time

before the LOW-to-HIGH transition of the

Clock, overrides the CEP, CET and PE inputs,

and causes the flip-flops to go LOW coinci-

The Master Reset (MR) is an asynchronous

overriding clear function which forces all sta-

ges to a LOW state while the MR input is

dent with the positive Clock transition.

LOW without regard to the Clock.

11 3 4 5 6 1 — U/\(\bar{D}\) PE D<sub>0</sub> D<sub>1</sub> D<sub>2</sub> D<sub>3</sub> 2 — CP TC 0~19 12 ~ 0 CEP TC 0~19 12 ~ 0 CET GC — 18

'I S569A

LOGIC SYMBOL

V<sub>CC</sub> = Pin 20 GND = Pin 10

The carry look-ahead circuitry provides for cascading counters for n-bit synchronous applications without additional gating. Instrumental in accomplishing this function are two Count Enable inputs ( $\overline{\text{CET}}\cdot\overline{\text{CEP}}$ ) and a Terminal Count ( $\overline{\text{TC}}$ ) output. Both Count Enable inputs must be LOW to count. The  $\overline{\text{CET}}$  input is fed forward to enable the  $\overline{\text{TC}}$  output. The  $\overline{\text{TC}}$  output thus enabled will produce a LOW output pulse with a duration approximately equal to the HIGH level portion of the  $Q_0$  output. This LOW level  $\overline{\text{TC}}$  pulse is used to enable successive cascaded stages. See Figure A in '168/'169 data sheet for the fast synchronous multistage counting connec

The Gated Clock output (GC) is a Terminal Count output which provides a HIGH-LOW-

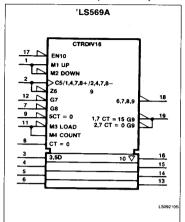

#### LOGIC SYMBOL (IEEE/IEC)

HIGH pulse for a duration equal to the LOW time of the Clock pulse when  $\overline{\text{TC}}$  is LOW. The GC output can be used as a Clock input for the next stage in a simple ripple expansion scheme

The direction of counting is controlled by the UP/DOWN (U/D) input; a HIGH will cause the count to increase, a LOW will cause the count to decrease.

The active LOW Output Enable ( $\overline{OE}$ ) input controls the 3-State buffer outputs independent of the counter operation. When  $\overline{OE}$  is LOW, the count appears at the buffer outputs. When  $\overline{OE}$  is HIGH, the outputs are in the HIGH impedance "off" state, which means they will neither drive nor load the bus.

# 74LS568A, 569A

### MODE SELECT — FUNCTION TABLE

|                         |    | INPUTS   |        |     |        |        |        | COUNTER STATES |                |                  |                |                |

|-------------------------|----|----------|--------|-----|--------|--------|--------|----------------|----------------|------------------|----------------|----------------|

| COUNTER OPERATING MODES | MR | СР       | SR     | U/D | PE     | CEP    | CET    | Dn             | Q <sub>0</sub> | Q <sub>1</sub>   | Q <sub>2</sub> | Q <sub>3</sub> |

| Asynchronous reset      | L  | Х        | х      | ×   | Х      | ×      | Х      | X              | L              | L                | L              | L              |

| Synchronous reset       | Н  | 1        | 1      | Х   | Х      | Х      | х      | Х              | L              | L                | L              | L              |

| Parallel load           | H  | <b>†</b> | h<br>h | X   | 1      | X      | X      | l<br>h         | L<br>H         | L<br>H           | L<br>H         | L<br>H         |

| Count up                | Н  | 1        | h      | h   | h      | 1      | ı      | Х              | cour           | nt up            |                |                |

| Count down              | Н  | 1        | h      | ı   | h      | 1      | ı      | Х              | cour           | nt down          |                |                |

| Hold (do nothing)       | H  | †        | h<br>h | X   | h<br>h | h<br>X | X<br>h | X<br>X         | 1              | change<br>change |                |                |

|                                |        | INPUTS                  | OUTPUTS                                                           |

|--------------------------------|--------|-------------------------|-------------------------------------------------------------------|

| 3-STATE BUFFER OPERATING MODES | ŌĒ     | Q <sub>n</sub> -Counter | Q <sub>0</sub> , Q <sub>1</sub> , Q <sub>2</sub> , Q <sub>3</sub> |

| Read counter                   | L<br>L | L<br>H                  | L<br>H                                                            |

| Disable outputs                | н      | L<br>H                  | (Z)<br>(Z)                                                        |

### **TERMINAL COUNT FUNCTION TABLE, '568A**

|    | INPU | INPUTS |     |     | COUNTER STATES |                |                |    | OUTPUTS |  |  |

|----|------|--------|-----|-----|----------------|----------------|----------------|----|---------|--|--|

| СР | U/D̄ | CEP    | CET | Qo  | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> | TC | GC      |  |  |

| Н  | L    | L      | L   | L   | L              | L              | L              | L  | Н       |  |  |

| Ë  | L    | L      | L   | . L | L              | L              | L              | L  | L       |  |  |

| X  | L    | н      | L   | L   | L              | L              | L              | L  | н       |  |  |

| X  | L    | ×      | Н   | ] L | L              | L              | L              | Н  | н       |  |  |

| H  | Н    | L      | L   | Н   | ×              | ×              | н              | L  | н       |  |  |

| Ĺ  | н    | L      | L   | Н   | x              | x              | н              | L  | L       |  |  |

| x  | l н  | н      | L   | н   | ×              | ×              | н              | L  | н       |  |  |

| X  | н    | X      | н   | н   | l x            | X              | Н              | н  | н       |  |  |

### **TERMINAL COUNT FUNCTION TABLE, '569A**

|    | INPUTS |     |     | COUNTER STATES |                |                |                | OUTPUTS |    |  |

|----|--------|-----|-----|----------------|----------------|----------------|----------------|---------|----|--|

| СР | U/D̄   | CEP | CET | Q <sub>0</sub> | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> | TC      | GC |  |

| Н  | L      | L   | L   | L              | L              | L              | L              | L       | Н  |  |

| Ĺ  | l L    | L   | L   | L              | L              | L              | L              | L       | L  |  |

| x  | L      | н   | L   | L              | L              | L              | L              | L       | н  |  |

| X  | L      | x   | н   | L              | L              | L              | L              | н       | Н  |  |

| Н  | н      | L   | L   | н              | н              | н              | н              | L       | Н  |  |

| L  | ĺн     | L   | L   | н              | н              | н              | Н              | L       | L  |  |

| ×  | н      | н   | L   | н              | н              | н              | н              | L       | H  |  |

| X  | н      | ×   | н   | H              | н              | н              | Н              | н       | н  |  |

= HIGH voltage level

= HIGH voltage level one set-up time prior to the LOW-to-HIGH clock transition = LOW voltage level

= LOW voltage level one set-up time prior to the LOW-to-HIGH clock transition = Don't care

(Z) = HIGH impedance "off" state

1 = LOW-to-HIGH clock transition

5-579

# 74LS568A, 569A

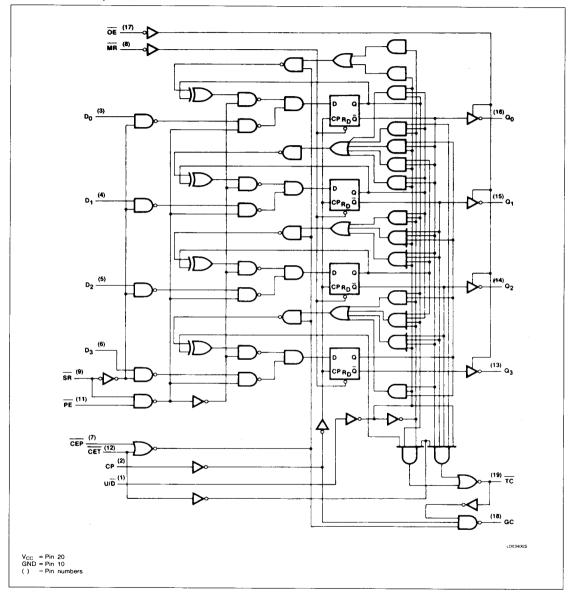

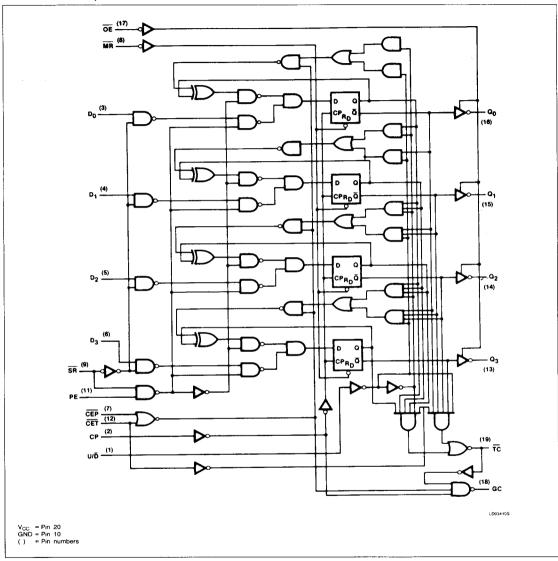

### LOGIC DIAGRAM, '568A

# 74LS568A, 569A

### LOGIC DIAGRAM, '569A

December 4, 1985 5-581

# 74LS568A, 569A

# ABSOLUTE MAXIMUM RATINGS (Over operating free-air temperature range unless otherwise noted.)

|                  | PARAMETER                                      | 74LS                     | UNIT |

|------------------|------------------------------------------------|--------------------------|------|

| V <sub>CC</sub>  | Supply voltage                                 | 7.0                      | V    |

| VIN              | Input voltage                                  | -0.5 to +7.0             | V    |

| I <sub>IN</sub>  | Input current                                  | -30 to +1                | mA   |

| V <sub>OUT</sub> | Voltage applied to output in HIGH output state | -0.5 to +V <sub>CC</sub> | V    |

| TA               | Operating free-air temperature range           | 0 to 70                  | °C   |

### RECOMMENDED OPERATING CONDITIONS

|                 | PARAME                         | TEO                             |      | 74LS |      |      |

|-----------------|--------------------------------|---------------------------------|------|------|------|------|

|                 | PARAME                         | IER                             | Min  | Nom  | Max  | UNIT |

| V <sub>CC</sub> | Supply voltage                 |                                 | 4.75 | 5.0  | 5.25 | V    |

| $V_{IH}$        | HIGH-level input voltage       |                                 | 2.0  |      |      | V    |

| VIL             | LOW-level input voltage        |                                 |      |      | +0.8 | V    |

| l <sub>iK</sub> | Input clamp current            |                                 |      |      | -18  | mA   |

| Іон             | HIGH-level output current      | Q <sub>0</sub> – Q <sub>3</sub> |      |      | -2.6 | mA   |

| -ОП             |                                | TC,GC                           |      |      | -400 | μА   |

| loL             | LOW-level output current       | Q <sub>0</sub> - Q <sub>3</sub> |      |      | 24   | mA   |

| ·OL             |                                | TC, GC                          |      |      | 8    | mA   |

| TA              | Operating free-air temperature |                                 | 0    |      | 70   | °C   |

# 74LS568A, 569A

#### DC ELECTRICAL CHARACTERISTICS (Over recommended operating free-air temperature range unless otherwise noted.)

|                  |                                                         |                                                  |                                 | 1                               | 74  | LS568, | 569  |      |

|------------------|---------------------------------------------------------|--------------------------------------------------|---------------------------------|---------------------------------|-----|--------|------|------|

|                  | PARAMETER                                               |                                                  | TEST CONDIT                     | TEST CONDITIONS                 |     |        | Max  | UNIT |

| .,               | LUCAL level systems with an                             | V <sub>CC</sub> = MIN,<br>V <sub>IH</sub> = MIN, | Q <sub>0</sub> – Q <sub>3</sub> | I <sub>OH</sub> = MAX           | 2.4 |        |      | v    |

| V <sub>OH</sub>  | HIGH-level output voltage                               | V <sub>IL</sub> = MAX,<br>I <sub>OH</sub> = MAX  | TC, GC                          | I <sub>OH</sub> = MAX           | 2.4 |        |      | v    |

|                  |                                                         |                                                  | 0 0                             | I <sub>OL</sub> = MAX           |     |        | 0.5  | ٧    |

|                  | 1 0 14 1 1 2 2 1 2 2 1 2 2 1 2 2 1 2 2 2 2              | V <sub>CC</sub> = MIN,                           | $Q_0 - Q_3$                     | I <sub>OL</sub> = 12mA (74LS)   |     |        | 0.5  | ٧    |

|                  | LOW-level output voltage                                | V <sub>IH</sub> = MIN,<br>V <sub>IL</sub> = MAX  | <del></del>                     | I <sub>OL</sub> = MAX           |     |        | 0.5  | V    |

|                  |                                                         |                                                  | TC, GC                          | I <sub>OL</sub> = 4mA (74LS)    |     |        | 0.4  | ٧    |

| VIK              | Input clamp voltage                                     | V <sub>CC</sub> = MIN, I <sub>1</sub> =          | l <sub>iK</sub>                 |                                 |     |        | -1.5 | ٧    |

| lozh             | Off-state output current,<br>HIGH-level voltage applied | V <sub>CC</sub> = MAX, V <sub>O</sub>            | = 2.7V                          |                                 |     |        | 20   | μΑ   |

| I <sub>OZL</sub> | Off-state output current,<br>LOW-level voltage applied  | V <sub>CC</sub> = MAX, V <sub>O</sub>            | = 0.4V                          |                                 |     |        | -20  | μΑ   |

| t <sub>i</sub>   | Input current at maximum input voltage                  | V <sub>CC</sub> = MAX, V <sub>I</sub>            | = 7.0V                          |                                 |     |        | 0.1  | mA   |

| I <sub>IH</sub>  | HIGH-level input current                                | V <sub>CC</sub> = MAX, V <sub>I</sub>            | = 2.7V                          |                                 |     |        | 20   | μA   |

| I <sub>IL</sub>  | LOW-level input current                                 | V <sub>CC</sub> = MAX, V <sub>I</sub>            | = 0.4V                          |                                 |     |        | -0.4 | mA   |

| los              | Short-circuit output current <sup>3</sup>               | V <sub>CC</sub> = MAX                            |                                 | Q <sub>0</sub> - Q <sub>3</sub> | -30 |        | -100 | mA   |

| ios              | Short Should Salpat Surrent                             | 1.00 14700                                       | TC, GC                          |                                 |     |        | -100 | mA   |

| loc              | Supply current (total)                                  | V <sub>CC</sub> = MAX                            |                                 | •                               |     | 28     | 43   | mA   |

#### NOTES:

<sup>1.</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

<sup>2.</sup> All typical values are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

<sup>3.</sup> los is tested with V<sub>OUT</sub> = +0.5V and V<sub>CC</sub> = V<sub>CC</sub> MAX +0.5V. Not more than one output should be shorted at a time and duration of the short circuit should not exceed one second.

# 74LS568A, 569A

### AC ELECTRICAL CHARACTERISTICS TA = 25°C, VCC = 5.0V

|                                      |                                      |                                  | 7-                    | 4LS                     |      |  |

|--------------------------------------|--------------------------------------|----------------------------------|-----------------------|-------------------------|------|--|

|                                      | PARAMETER                            | TEST CONDITIONS                  | C <sub>L</sub> = 45pF | , R <sub>L</sub> = 667Ω | UNIT |  |

|                                      |                                      |                                  | Min                   | Max                     |      |  |

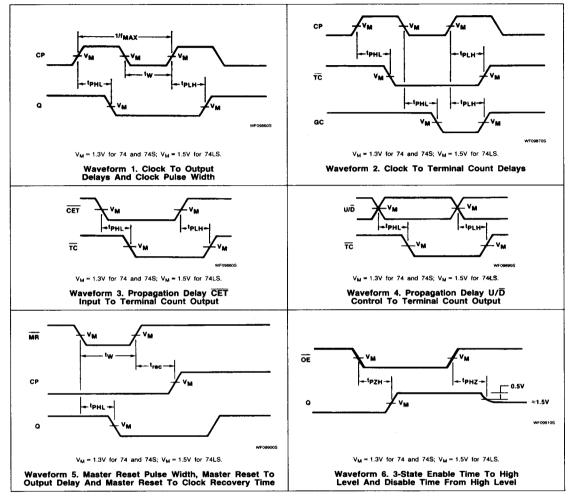

| f <sub>MAX</sub>                     | Maximum clock frequency              | Waveform 1                       | 35                    |                         | MHz  |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>Clock to output | Waveform 1                       |                       | 15<br>20                | ns   |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>Clock to TC     | Waveform 2                       |                       | 20<br>25                | ns   |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay CET to TC          | Waveform 3                       |                       | 14<br>15                | ns   |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay U/D control to TC  | Waveform 4                       |                       | 20<br>25                | ns   |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>Clock to GC     | Waveform 2                       |                       | 15<br>17                | ns   |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | CET or CEP to GC                     | Waveform 2                       |                       | 16<br>26                | ns   |  |

| t <sub>PHL</sub>                     | Propagation delay MR to output       | Waveform 5                       |                       | 20                      | ns   |  |

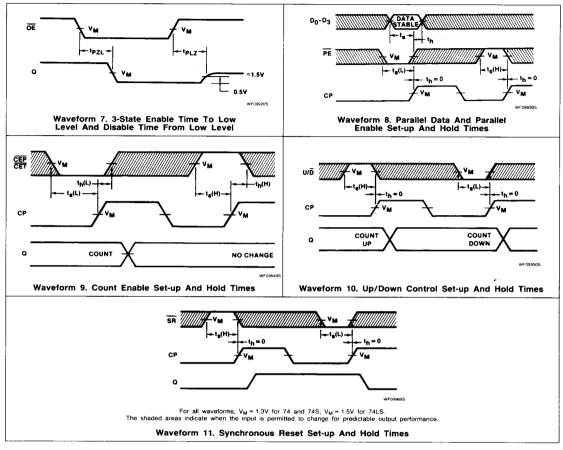

| t <sub>PZH</sub>                     | Output enable to HiGH level          | Waveform 6                       |                       | 15                      | ns   |  |

| t <sub>PZL</sub>                     | Output enable to LOW level           | Waveform 7                       |                       | 15                      | ns   |  |

| t <sub>PHZ</sub>                     | Output disable from HIGH level       | Waveform 6, C <sub>L</sub> = 5pF |                       | 20                      | ns   |  |

| t <sub>PLZ</sub>                     | Output disable from LOW level        | Waveform 7, C <sub>L</sub> = 5pF |                       | 22                      | ns   |  |

#### NOTES:

### AC SET-UP REQUIREMENTS $T_A = 25$ °C, $V_{CC} = 5.0$ V

|                  | PARAMETER                      | TEST CONDITIONS | 74  | LS  |      |

|------------------|--------------------------------|-----------------|-----|-----|------|

|                  | PANAMETER                      | TEST CONDITIONS | Min | Max | UNIT |

| t <sub>W</sub>   | Clock pulse width              | Waveform 1      | 20  |     | ns   |

| ts               | Set-up time data to clock      | Waveform 8      | 20  |     | ns   |

| t <sub>h</sub>   | Hold time data to clock        | Waveform 8      | 0   |     | ns   |

| ts               | Set-up time PE to clock        | Waveform 8      | 25  |     | ns   |

| th               | Hold time PE to clock          | Waveform 8      | 0   |     | ns   |

| t <sub>S</sub>   | Set-up time CEP & CET to clock | Waveform 9      | 20  |     | ns   |

| th               | Hold time CEP & CET to clock   | Waveform 9      | 0   |     | ns   |

| ts               | Set-up time U/D to clock       | Waveform 10     | 30  |     | ns   |

| t <sub>h</sub>   | Hold time U/D to clock         | Waveform 10     | 0   |     | ns   |

| ts               | Set-up time SR to clock        | Waveform 11     | 30  |     | ns   |

| th               | Hold time SR to clock          | Waveform 11     | 0   |     | ns   |

| t <sub>rec</sub> | Recovery time MR to clock      | Waveform 5      | 20  |     | ns   |

<sup>1.</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

<sup>2.</sup> All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25$ °C.

<sup>3.</sup> Ios is tested with V<sub>OUT</sub> = + 0.5V and V<sub>CC</sub> = V<sub>CC</sub> MAX + 0.5V. Not more than one output should be shorted at a time and duration of the short circuit should not exceed one second.

# 74LS568A, 569A

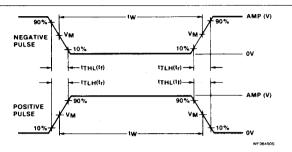

#### **AC WAVEFORMS**

# 74LS568A, 569A

### **AC WAVEFORMS (Continued)**

# 74LS568A, 569A

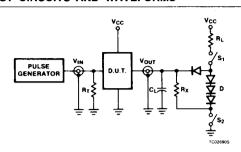

#### TEST CIRCUITS AND WAVEFORMS

$V_M \approx 1.3V$  for 74LS;  $V_M = 1.5V$  for all other TTL families.

### Test Circuit For 3-State Outputs

## SWITCH POSITION

| TEST             | SWITCH 1 | SWITCH 2 |

|------------------|----------|----------|

| t <sub>PZH</sub> | Open     | Closed   |

| t <sub>PZL</sub> | Closed   | Open     |

| t <sub>PHZ</sub> | Closed   | Closed   |

| t <sub>PLZ</sub> | Closed   | Closed   |

DEFINITIONS

R<sub>L</sub> = Load resistor to V<sub>CC</sub>; see AC CHARACTERISTICS for value.

$C_L = Load$  capacitance includes jig and probe capacitance; see AC CHARACTERISTICS for value.

R<sub>T</sub> = Termination resistance should be equal to Z<sub>OUT</sub> of Pulse Generators.

D = Diodes are 1N916, 1N3064, or equivalent.

$B_X = 1k\Omega$  for 74, 74S,  $B_X = 5k\Omega$  for 74LS.

$t_{\mathsf{TLH}},\ t_{\mathsf{THL}}$  Values should be less than or equal to the table entries.

| FAMILY | INPUT PULSE REQUIREMENTS |           |             |                  |                  |  |

|--------|--------------------------|-----------|-------------|------------------|------------------|--|

|        | Amplitude                | Rep. Rate | Pulse Width | t <sub>TLH</sub> | t <sub>THL</sub> |  |

| 74     | 3.0V                     | 1MHz      | 500ns       | 7ns              | 7ns              |  |

| 74LS   | 3.0V                     | 1MHz      | 500ns       | 15ns             | 6ns              |  |

| 748    | 3.0V                     | 1MHz      | 500ns       | 2:5ns            | 2.5ns            |  |