# REMOTE CONTROL SYSTEM FOR INFRARED OPERATION

The SAF1032P (receiver/decoder) and the SAF1039P (transmitter) form the basic parts of a sophisticated remote control system (pcm: pulse code modulation) for infrared operation. The ICs can be used, for example, in TV, audio, industrial equipment, etc.

Features:

### SAF1032P receiver/decoder:

- 16 programme selection codes

- automatic preset to stand-by at power 'ON', including automatic analogue base settings to 50% and automatic preset of programme selection '1' code

- 3 analogue function controls, each with 63 steps

- single supply voltage

- protection against corrupt codes.

#### SAF1039P transmitter:

- 32 different control commands

- static keyboard matrix

- current drains from battery only during key closure time

- two transmission modes selectable.

The devices are implemented in LOCMOS (Local Oxidation Complementary MOS) technology to achieve an extremely low power consumption.

Inputs and outputs are protected against electrostatic effects in a wide variety of device-handling situations. However, to be totally safe, it is desirable to take handling precautions into account.

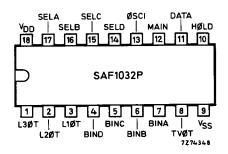

Fig. 1 Pin designations.

### **PACKAGE OUTLINES**

SAF1032P: 18-lead DIL; plastic (SOT102). SAF1039P: 16-lead DIL; plastic (SOT38Z).

# SAF1032P SAF1039P

## **PINNING**

8

$V_{SS}$

To facilitate easy function recognition, each integrated circuit pin has been allocated a code as shown below.

| SAF | 1032P    |                                  |    |          |                          |

|-----|----------|----------------------------------|----|----------|--------------------------|

| 1   | L3ØT     | linear output                    | 10 | HØLD     | control input            |

| 2   | L2ØT     | linear output                    | 11 | DATA     | data input               |

| 3   | L1ØT     | linear output                    | 12 | MAIN     | reset input              |

| 4   | BIND     | binary 8 output                  | 13 | ØSCI     | clock input              |

| 5   | BINC     | binary 4 output                  | 14 | SELD     | binary 8 output          |

| 6   | BINB     | binary 2 output                  | 15 | SELC     | binary 4 output          |

| 7   | BINA     | binary 1 output                  | 16 | SELB     | binary 2 output          |

| 8   | T∨ØT     | on/off input/output              | 17 | SELA     | binary 1 output          |

| 9   | $v_{SS}$ |                                  | 18 | $v_{DD}$ |                          |

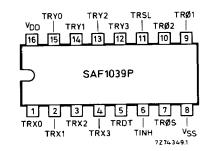

| SAF | 1039P    |                                  |    |          |                          |

| 1   | TRX0     | keyboard input                   | 9  | TRØ1     | oscillator control input |

| 2   | TRX1     | keyboard input                   | 10 | TRØ2     | oscillator control input |

| 3   | TRX2     | keyboard input                   | 11 | TRSL     | keyboard select line     |

| 4   | TRX3     | keyboard input                   | 12 | TRY3     | keyboard input           |

| 5   | TRDT     | data output                      | 13 | TRY2     | keyboard input           |

| 6   | TINH     | inhibit output/mode select input | 14 | TRY1     | keyboard input           |

| 7   | TRØS     | oscillator output                | 15 | TRY0     | keyboard input           |

| _   |          | •                                |    |          |                          |

16

$V_{DD}$

#### BASIC OPERATING PRINCIPLES

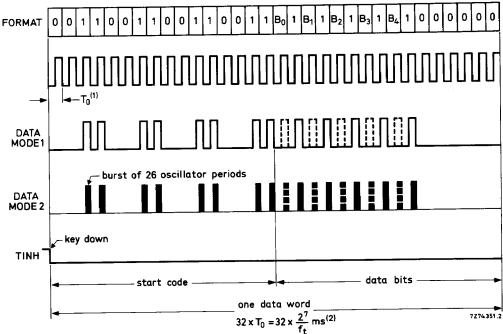

The data to be transmitted are arranged as serial information with a fixed pattern (see Fig. 2), in which the data bit-locations B<sub>0</sub> to B<sub>4</sub> represent the generated key-command code. To cope with IR (infrared) interferences of other sources a selective data transmission is present. Each transmitted bit has a burst of 26 oscillator periods.

Before any operation will be executed in the receiver/decoder chip, the transmitted data must be accepted twice in sequence. This means the start code must be recognized each time a data word is applied and comparison must be true between the data bits of two successively received data words. If both requirements are met, one group of binary output buffers will be loaded with a code defined by the stored data bits, and an internal operation can also take place. See operating code table.

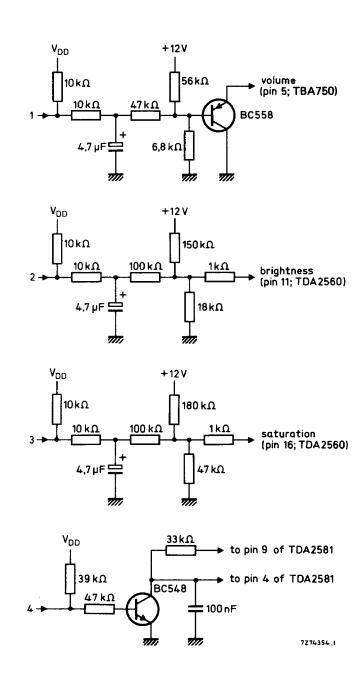

The contents of the 3 analogue function registers are available on the three outputs in a pulse code versus time modulation format after D (digital) to A (analogue) conversion. The proper analogue levels can be obtained by using simple integrated networks. For local control a second transmitter chip (SAF1039P) is used (see Fig. 7).

(1)  $T_0 = 1$  clock period = 128 oscillator periods. (2)  $f_t$  in kHz.

Fig. 2 Pattern for data to be transmitted.

#### TIMING CONSIDERATIONS

The transmitter and receiver operate at different oscillator frequencies. Due to the design neither frequency is very critical, but correlation between them must exist. Calculation of these timing requirements shows the following.

With a tolerance of  $\pm 10\%$  on the oscillator frequency (f<sub>t</sub>) of the transmitter, the receiver oscillator frequency (f<sub>r</sub> = 3 x f<sub>t</sub>) must be kept constant with a tolerance of  $\pm 20\%$ .

On the other hand, the data pulse generated by the pulse stretcher circuit (at the receiver side) may vary  $\pm 25\%$  in duration.

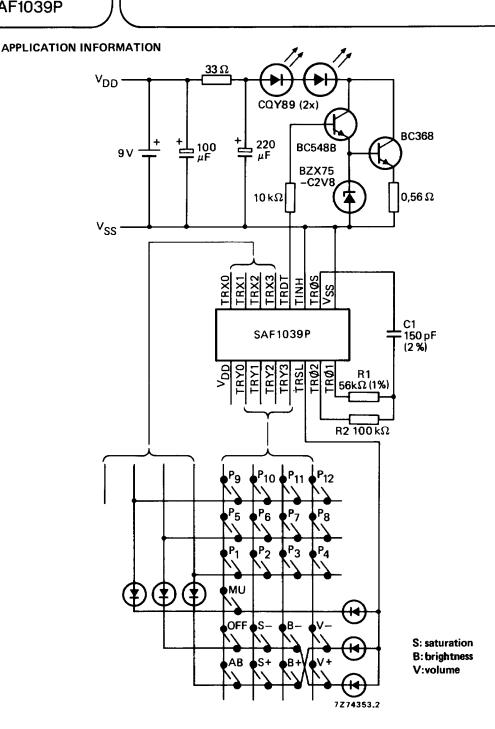

### GENERAL DESCRIPTION OF THE SAF1039P TRANSMITTER

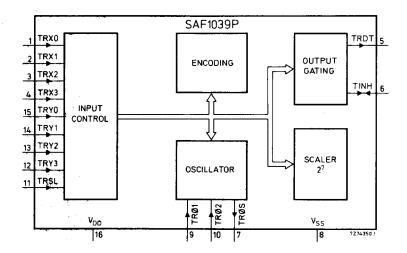

Fig. 3 Block diagram of SAF1039P transmitter.

Any keyboard activity on the inputs TRX0 to TRX3, TRY0 to TRY3 and TRSL will be detected. For a legal key depression, one key down at a time (one TRX and TRY input activated), the oscillator starts running and a data word, as shown on the previous page, is generated and supplied to the output TRDT. If none, or more than 2 inputs are activated at the same time, the input detection logic of the chip will generate an overall reset and the oscillator stops running (no legal key operation).

This means that for each key-bounce the logic will be reset, and by releasing a key the transmitted data are stopped at once.

The minimum key contact time required is the duration of two data words. The on-chip oscillator is frequency controlled with the external components R1 and C1 (see circuit Fig. 6); the addition of resistor R2 means that the oscillator frequency is practically independent of supply voltage variations. A complete data word is arranged as shown in Fig. 2, and has a length of  $32 \times T_0$  ms, where  $T_0 = 2^7/f_{\uparrow}$ .

#### Operation mode

|     | DATA                                                   | FUNCTION OF TINH                                                                         |

|-----|--------------------------------------------------------|------------------------------------------------------------------------------------------|

| 1 2 | unmodulated: LOCAL operation modulated: REMOTE control | output, external pull-up resistor to V <sub>DD</sub> input, connected to V <sub>SS</sub> |

## GENERAL DESCRIPTION OF THE SAF1032P RECEIVER/DECODER

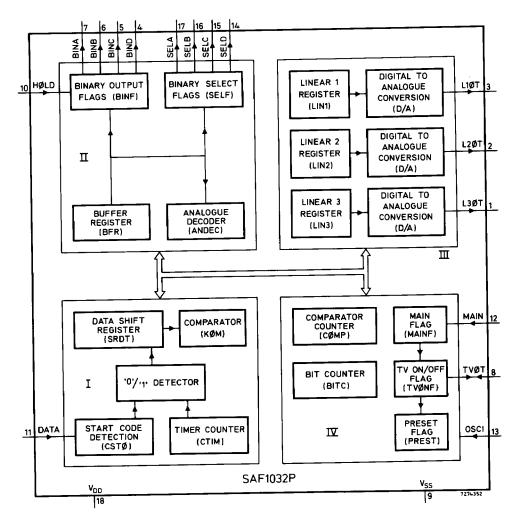

Fig. 4 Block diagram of SAF1032P receiver/decoder.

The logic circuitry of the receiver/decoder chip is divided into four main parts as shown in the block diagram above.

#### Part I

This part decodes the applied DATA information into logic '1' and '0'. It also recognizes the start code and compares the stored data-bits with the new data-bits accepted.

#### Part II

This part stores the programme selection code in the output group (BINF) and memorizes it for condition  $H\emptyset LD = LOW$ .

It puts the functional code to output group (SELF) during data accept time, and decodes the internally used analogue commands (ANDEC).

#### Part III

This part controls the analogue function registers (each 6-bits long), and connects the contents of the three registers to the analogue outputs by means of D/A conversion. During sound mute, output L1ØT will be forced to HIGH level.

#### Part IV

This part keeps track for correct power 'ON' operation, and puts chip in 'stand-by' condition at supply voltage interruptions.

The logic design is dynamic and synchronous with the clock frequency (ØSCI), while the required control timing signals are derived from the bit counter (BITC).

#### Operation

Serial information applied to the DATA input will be translated into logic '1' and '0' by means of a time ratio detector.

After recognizing the start code (CSTØ) of the data word, the data bits will be loaded into the data shift register (SRDT). At the first trailing edge of the following data word a comparison (KØM) takes place between the contents of SRDT and the buffer register (BFR). If SRDT equals BFR, the required operation will be executed under control of the comparator counter (CØMP).

As shown in the operating code table on the next page, the 4-bit wide binary output buffer (BINF) will be loaded for BFR0 = '0', while for BFR0 = '1' the binary output buffer (SELF), also 4-bit wide will be activated during the data accept time.

At the same time operations involving the internal commands are executed. The contents of the analogue function registers (each 6-bits long) are controlled over 63 steps, with minimum and maximum detection, while the D/A conversion results in a pulsed output signal with a conversion period of 384 clock periods (see Fig. 5).

First power 'ON' will always put the chip in the 'stand-by' position. This results in an internal clearing of all logic circuitry and a 50% presetting of the contents of the analogue registers (analogue base value). The programme selection '1' code will also be prepared and all the outputs will be non-active (see operating output code table).

From 'stand-by' the chip can be made operational via a programme selection command, generated LOCAL or via REMOTE, or directly by forcing the TV ON/OFF output (TVØT) to zero for at least 2 clock periods of the oscillator frequency.

For POWER ON RESET a negative-going pulse should be applied to input MAIN, when  $V_{DD}$  is stabilized; pulse width LOW  $\geq$  100  $\mu$ s.

Fig. 5 Analogue output pulses.

## **OPERATING CODE TABLE**

|                                      | ey-matr<br>positio                   |                                 |               | buffer<br>BFR                   |                                 |                                 |                                 |                            | BINF SELF<br>(BIN.) (SEL.) |                                 |                                 |                                 |                                 | function                        |                                 |                                                                                                                                        |

|--------------------------------------|--------------------------------------|---------------------------------|---------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|----------------------------|----------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| TRX.                                 | TRY.                                 | TRSL                            | 0             | 1                               | 2                               | 3                               | 4                               | Α                          | В                          | С                               | D                               | Α                               | В                               | _C                              | D                               |                                                                                                                                        |

| 0<br>0<br>0<br>0<br>1                | 0<br>1<br>2<br>3<br>0                | 0 0 0 0 0 0                     | 0 0 0 0 0     | 0<br>0<br>0<br>0<br>1           | 1<br>0<br>1<br>0<br>1           | 1<br>1<br>0<br>0<br>1<br>1      | 000000                          | 0<br>1<br>0<br>1<br>0      | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>0<br>0<br>0<br>1           | 0 0 0 0 0 0                     | 1<br>1<br>1<br>1<br>1           | 1<br>1<br>1<br>1<br>1<br>1      | 1<br>1<br>1<br>1<br>1<br>1      | 1<br>1<br>1<br>1<br>1           | programme<br>select + ON                                                                                                               |

| 1 1                                  | 2<br>3                               | 0<br>0                          | 0             | 1<br>1                          | 1<br>0                          | 0                               | 0                               | 0                          | 1                          | 1<br>1                          | 0                               | 1                               | 1                               | 1                               | 1                               | J                                                                                                                                      |

| 2<br>2<br>2<br>2<br>3<br>3<br>3<br>3 | 0<br>1<br>2<br>3<br>0<br>1<br>2<br>3 | 0<br>0<br>0<br>0<br>0<br>0      | 0000000       | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 1<br>0<br>1<br>0<br>1<br>0      | 1<br>1<br>0<br>0<br>1<br>1<br>0 | 1<br>1<br>1<br>1<br>1<br>1      | 0<br>1<br>0<br>1<br>0<br>1 | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1<br>1 | 1 1 1 1 1 1 1                   | 1<br>1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1<br>1 | programme<br>select + ON                                                                                                               |

| 0<br>0<br>0<br>0<br>1<br>1<br>1      | 0<br>1<br>2<br>3<br>0<br>1<br>2<br>3 | 1<br>1<br>1<br>1<br>1<br>1      | 1 1 1 1 1 1 1 | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 1<br>0<br>1<br>0<br>1<br>0<br>1 | 1<br>0<br>0<br>1<br>1<br>0      | 0<br>0<br>0<br>0<br>0<br>0      | X<br>X<br>X<br>O<br>X<br>X | X<br>X<br>X<br>0<br>X<br>X | X<br>X<br>X<br>0<br>X<br>X      | X<br>X<br>X<br>0<br>X<br>X      | 0<br>0<br>0<br>0<br>1<br>1      | 1<br>0<br>1<br>0<br>0<br>0      | 1<br>1<br>0<br>0<br>0<br>1<br>0 | 1<br>1<br>1<br>0<br>1<br>1      | analogue base<br>reg. (LIN3) + 1<br>reg. (LIN2) + 1<br>reg. (LIN1) + 1<br>OFF<br>reg. (LIN3) - 1<br>reg. (LIN2) - 1<br>reg. (LIN1) - 1 |

| 2<br>2<br>2<br>2<br>3<br>3<br>3<br>3 | 0<br>1<br>2<br>3<br>0<br>1<br>2<br>3 | 1<br>1<br>1<br>1<br>1<br>1<br>1 | 1 1 1 1 1 1   | 0<br>0<br>0<br>1<br>1<br>1      | 1<br>0<br>1<br>0<br>1<br>0<br>1 | 1<br>0<br>0<br>1<br>1<br>0      | 1<br>1<br>1<br>1<br>1<br>1<br>1 | X<br>X<br>X<br>X<br>X      | X<br>X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X<br>X      | X<br>X<br>X<br>X<br>X<br>X      | 0<br>0<br>0<br>0<br>1<br>1<br>1 | 1<br>0<br>1<br>0<br>1<br>0      | 1<br>1<br>0<br>0<br>1<br>1<br>0 | 0<br>0<br>0<br>0<br>0<br>0      | mute (set/reset)                                                                                                                       |

## Note

Reset mute also on programme select codes, (LIN1)  $\pm$  1, and analogue base.

## **OPERATING OUTPUT CODE**

|                                         |   | (BIN.) |   |   |   | (SEL.) |   |   |   | L.ØT) |   |      |  |

|-----------------------------------------|---|--------|---|---|---|--------|---|---|---|-------|---|------|--|

|                                         | Α | В      | С | D | Α | В      | С | D | 1 | 2     | 3 | TVØT |  |

| 'stand-by' OFF<br>via remote            | 0 | 0      | 0 | 0 | 0 | 0      | 0 | 0 | 1 | 0     | 0 | 1    |  |

| ON — 'not hold' condition non-operating | 1 | 1      | 1 | 1 | 1 | 1      | 1 | 1 | × | X     | х | 0    |  |

| ON — 'hold' condition non-operating     | × | х      | x | х | 1 | 1      | 1 | 1 | × | х     | х | 0    |  |

## **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| Supply voltage                  | $v_{DD}-v_{S}$   | S -0,5 | to 11 V |

|---------------------------------|------------------|--------|---------|

| Input voltage                   | V <sub>I</sub>   | max.   | 11 V    |

| Current into any terminal       | ±I <sub>I</sub>  | max.   | 10 mA   |

| Power dissipation (per output)  | $P_{o}$          | max.   | 50 mW   |

| Power dissipation (per package) | P <sub>tot</sub> | max.   | 200 mW  |

| Operating ambient temperature   | $T_{amb}$        | -40 to | +85 °C  |

| Storage temperature             | T <sub>stg</sub> | −65 to | +150 °C |

## **CHARACTERISTICS**

T<sub>amb</sub> = 0 to +85 °C (unless otherwise specified)

## SAF1039P only

|                                                                                                                                 | symbol          | min.                    | typ.                      | max.                                       |                          | V <sub>DD</sub>          | T <sub>amb</sub><br>°C |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|---------------------------|--------------------------------------------|--------------------------|--------------------------|------------------------|

| Recommended supply voltage                                                                                                      | V <sub>DD</sub> | 7                       | _                         | 10                                         | ٧                        |                          |                        |

| Supply current quiescent                                                                                                        | l <sub>DD</sub> |                         | _<br>1                    | 10<br>50                                   | μ <b>Α</b><br>μ <b>Α</b> | 10<br>7                  | 25<br>65               |

| operating; TRØ1 at V <sub>SS</sub> ;<br>outputs unloaded;<br>one keyboard switch<br>closed                                      | lDD             |                         | _<br>0,8                  | 1,7                                        | mA<br>mA                 | 10<br>10                 | all<br>25              |

| Inputs (note 1) TRØ2; TINH (note 2) input voltage HIGH input voltage LOW input current                                          | VIH<br>VIL      | 0,8V <sub>DD</sub><br>0 | -<br><br>10 <sup>-5</sup> | V <sub>DD</sub><br>0,2V <sub>DD</sub><br>1 | V<br>V<br>μΑ             | 7 to 10<br>7 to 10<br>10 | all<br>all<br>25       |

| Outputs TRDT; TRØS; TRØ1 output current HIGH at VOH = VDD -0,5 V                                                                | -lон            | 0,4                     | _                         | _                                          | mA                       | 7                        | all                    |

| output current LOW<br>at VOL = 0,4 V                                                                                            | <sup>1</sup> OL | 0,4                     | _                         | _                                          | mA                       | 7                        | all                    |

| TRDT output leakage current when disabled VO = VSS to VDD TINH                                                                  | lor             | _                       | _                         | 1                                          | <b>μ</b> Α :             | 10                       | 25                     |

| output current LOW<br>VOI = 0,4 V                                                                                               | loL             | 0,4                     | _                         | _                                          | mA                       | 7                        | all                    |

| Oscillator<br>maximum oscillator<br>frequency                                                                                   | fosc            | 120                     | _                         | _                                          | kHz                      |                          |                        |

| frequency variation with<br>supply voltage, temperature<br>and spread of IC properties<br>at f <sub>nom</sub> = 36 kHz (note 3) | Δf              | _                       | _                         | 0,15f <sub>nor</sub>                       | n                        | 7 to 10                  | all                    |

| oscillator current drain<br>at f <sub>nom</sub> = 36 kHz                                                                        | losc            | _                       | 1,3                       | 2,5                                        | mΑ                       | 10                       | 25                     |

# SAF1032P SAF1039P

## **CHARACTERISTICS**

$T_{amb} = 0$  to +85 °C (unless otherwise specified)

## SAF1032P only

|                                                                                                                                                    | symbol                             | min.                                     | typ.             | max.                                     |            | V <sub>DD</sub><br>V | T <sub>amb</sub><br>°C |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------|------------------|------------------------------------------|------------|----------------------|------------------------|

| Recommended supply voltage Supply current                                                                                                          | V <sub>DD</sub>                    | 8                                        | -                | 10                                       | ٧          |                      |                        |

| quiescent                                                                                                                                          | ۵۵۱                                | _<br>_                                   | _<br>1           | 50<br>300                                | μΑ<br>μΑ   | 10<br>10             | 25<br>85               |

| operating; I <sub>O</sub> = 0; at<br>ØSCI frequency of 100 kHz                                                                                     | IDD                                | _                                        |                  | 1                                        | mA         | 10                   | all                    |

| Inputs DATA; ØSCI; HØLD; TVØT (see note 4) input voltage HIGH input voltage LOW                                                                    | V <sub>IH</sub><br>V <sub>IL</sub> | 0,7V <sub>DD</sub><br>0                  | _<br>_           | V <sub>DD</sub><br>0,2V <sub>DD</sub>    | <b>V V</b> | 8 to 10<br>8 to 10   | all<br>all             |

| MAIN; tripping levels<br>input voltage increasing<br>input voltage decreasing                                                                      | V <sub>ti</sub><br>V <sub>td</sub> | 0,4V <sub>DD</sub><br>0,1V <sub>DD</sub> | _<br>_           | 0,9V <sub>DD</sub><br>0,6V <sub>DD</sub> | V<br>V     | 5 to 10<br>5 to 10   | all<br>all             |

| input current; all inputs except TVØT                                                                                                              | Ц                                  | _                                        | 10 <sup>-5</sup> | 1                                        | μΑ         | 10                   | 25                     |

| input signal rise and fall<br>times (10% and 90% V <sub>DD</sub> )<br>all inputs except MAIN                                                       | t <sub>r</sub> , t <sub>f</sub>    | _                                        | -                | 5                                        | μs         | 8 to 10              | ali                    |

| Outputs programme selection: BINA/B/C/D auxiliary: SELA/B/C/D analogue: L3ØT; L2ØT; L1ØT TVØT (note 4) all open drain n-channel output current LOW |                                    | 16                                       |                  |                                          | mA         | 8                    | all                    |

| at V <sub>OL</sub> = 0,4 V<br>output leakage current                                                                                               | lor                                | 1,6                                      | _                | _                                        | mA         | _                    |                        |

| at $V_0 = V_{SS}$ to $V_{DD}$                                                                                                                      | lOL                                | -                                        | _                | 10                                       | μΑ         | 10                   | all                    |

For note 4 see next page.

#### Notes to characteristics

1. The keyboard inputs (TRX.; TRY.; TRSL) are not voltage driven (see application information diagram Fig. 6).

If one key is depressed, the circuit generates the corresponding code. The number of keys depressed at a time, and this being recognized by the circuit as an illegal operation, depends on the supply voltage (V<sub>DD</sub>) and the leakage current (between device and printed-circuit board) externally applied to the keyboard inputs.

If no leakage is assumed, the circuit recognizes an operation as illegal for any number of keys > 1 depressed at the same time with  $V_{DD}$  = 7 V. At a leakage due to a 1 M $\Omega$  resistor connected to each keyboard input and returned to either  $V_{DD}$  or  $V_{SS}$ , the circuit recognizes at least 2 keys depressed at a time with  $V_{DD}$  = 7 V.

The highest permissible values of the contact series resistance of the keyboard switches is 500  $\Omega$ .

- 2. Inhibit output transistor disabled.

- 3.  $\Delta f$  is the width of the distribution curve at 2  $\sigma$  points ( $\sigma$  = standard deviation).

- 4. Terminal TVØT is input for manual 'ON'. When applying a LOW level TVØT becomes an output carrying a LOW level.

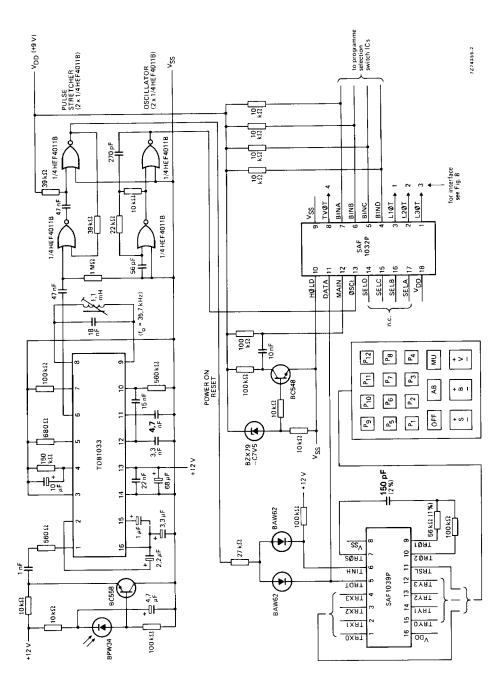

Fig. 6 Interconnection diagram of transmitter circuit SAF1039P in a remote control system, for a television receiver with 12 programmes.

**798** June 1981

Fig. 7 Interconnection diagram showing the SAF1032P and SAF1039P used in a TV control system.

Fig. 8 Additional circuits from outputs L1ØT (1), L2ØT (2), L3ØT (3) and TVØT (4) of the SAF1032P in circuit of Fig. 7.